- ALL COMPUTER, ELECTRONICS AND MECHANICAL COURSES AVAILABLE…. PROJECT GUIDANCE SINCE 2004. FOR FURTHER DETAILS CALL 9443117328

Projects > ELECTRONICS > 2017 > IEEE > VLSI

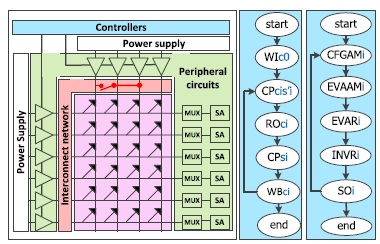

Today’s computer architectures suffer from many challenges, such as the near end of CMOS downscaling, the memory/communication bottleneck, the power wall, and the programming complexity. As a consequence, these architectures become inefficient in solving big data problems or general data intensive applications. Computation-in-memory (CIM) is a novel architecture that tries to solve/alleviate the impact of these challenges using the same device (i.e., the memristor) to implement the processor and memory in the same physical crossbar. In order to analyze its feasibility in depth, this paper proposes two memristor implementations of a data intensive arithmetic application (i.e., parallel addition). To the best of our knowledge, this is the first paper that considers the cost of the entire architecture including both crossbar and its CMOS controller.

Convolutional Neural Network.

In this paper, we showed two memristor crossbar implementations of CIM parallel adder. CIM alleviates the memory bottleneck by utilizing the memristor devices in the crossbar for both computation and storage. We analyzed for both implementations (one based on Boolean logic and the other on implication logic) their impact on the total cost. This cost includes the delay, energy, and area of the crossbar, interconnect network, peripheral circuit, and CMOS controller. Our results show that the implementation of both designs is feasible. In fact, a tradeoff can be made between the performance and resource usage. Finally, the results also show that CIM architecture efficiently deals with large-scale problems. In comparison, the memristor implementation outperforms a similar multicore implementation by at least two orders of magnitude in terms of energy delay efficiency, energy efficiency, and area efficiency. In short, CIM is a viable candidate for next generation computers.

CIM Parallel Adder