- ALL COMPUTER, ELECTRONICS AND MECHANICAL COURSES AVAILABLE…. PROJECT GUIDANCE SINCE 2004. FOR FURTHER DETAILS CALL 9443117328

Projects > ELECTRICAL > 2017 > IEEE > POWER SYSTEMS

This paper proposes a selective voltage harmonic compensation strategy for stand-alone inverters. The use of LC output filters makes it possible to reduce switching harmonics at the output terminals of the inverter, however it also produces voltage distortion when feeding non-linear loads due to the harmonic voltage drop across the filter inductances. To compensate the voltage harmonic distortion and produce sinusoidal voltage, it is proposed to add virtual impedances to the fundamental voltage control. The whole process and considerations for the impedance design are described and a stability analysis of the system is presented.

Selective Harmonic Mitigation Technique.

This paper proposes a selective voltage harmonic compensation method based on virtual impedances in which the virtual impedance takes account of the delays caused by measuring, filtering and computation, the need for damping, and the parasitic elements of the electrical components. Implementation of this impedance achieves an individual reduction in the harmonic component values using virtual impedances and THD reduction, which are similar values to those obtained by closed loop techniques proposed in the literature. Therefore, it has been proved that the proposed virtual impedance achieves effective compensation, without requiring high sampling frequencies to achieve effective compensation, which allows its branched implementation.

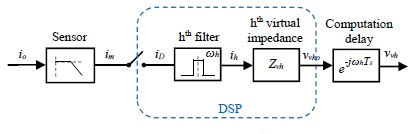

Block diagram of compensation method based on virtual impedances

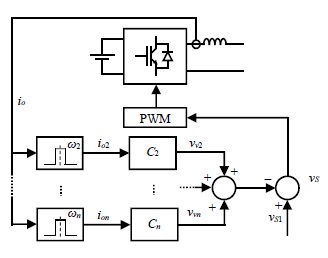

Proposed control diagram for harmonic