- ALL COMPUTER, ELECTRONICS AND MECHANICAL COURSES AVAILABLE…. PROJECT GUIDANCE SINCE 2004. FOR FURTHER DETAILS CALL 9443117328

Projects > ELECTRONICS > 2017 > IEEE > VLSI

Due to the conventional look-up-table (LUT) using the static random access memory (SRAM) cell, field programmable gate arrays (FPGAs) almost reach the limitation in term of the density, speed and configuration overhead. This paper proposes an improved memristor-based look-up-table (MLUT) circuit which is compatible with the mainstream LUT circuit in FPGA. Any arbitrary combined logic functions can be implemented in the MLUT through specific configurations. Then the MLUT shows superior advantages over the conventional LUT such as smaller area overhead and fewer data transmission. As a case study, a one-bit full adder is simulated to verify that the design is of practice in PSPICE. Moreover, the adder can be cascaded into multi-bit full adder demonstrating competitiveness against the conventional configurable logic block in FPGA technology. MLUT can be a candidate to replace the conventional SRAM-based LUT and further improves the performance of FPGAs.

Optimization.

The detailed memristor-based LUT design is put forward in this paper. The circuit and sub-circuit performance are analyzed. In this study, a MLUT-based simplified CLB of FPGA is proposed and simulated. Combining memristor and CMOS, a configurable logic block architecture with possible higher density and better efficiency is revealed. The conventional CLB of FPGA is depicted briefly, then reviews about memristor and the combination with CMOS technology are given. The circuit design of MLUT in FPGA using memristor-CMOS hybrid approach is presented.

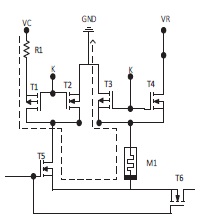

Schematic of the computing mode circuit current flow (K=0)

Schematic of the configuring mode circuit current flow (K=1)

Detailed schematic of memristor-based two-input look-up-tables