- ALL COMPUTER, ELECTRONICS AND MECHANICAL COURSES AVAILABLE…. PROJECT GUIDANCE SINCE 2004. FOR FURTHER DETAILS CALL 9443117328

Projects > ELECTRONICS > 2017 > IEEE > VLSI

In this brief, a novel two-extra-column trellis min–max algorithm and the decoder architecture based on only the first minimum values are proposed for nonbinary low-density parity-check (NB-LDPC) codes. The algorithm greatly reduces the hardware complexity and improves the latency as well as the throughput of the proposed decoder architecture compared with the previous works. A layered decoder architecture based on the proposed algorithm for (837, 726) NB-LDPC code over GF(32) is implemented with a 90-nm CMOS technology.

Decoding Algorithm, Simplified Min-Sum Algorithm.

This paper has proposed the TEC-TMM algorithm to reduce greatly the hardware complexity of the CNU architecture and provide an improvement of the error-correcting performance. In addition, an efficient layered NB-LDPC decoder architecture based on the proposed algorithm is presented. In this brief, a novel two-extra-column TMM (TEC-TMM) algorithm based on only the first minimum values for the NB-LDPC codes is proposed. This algorithm eliminates the second minimum values in the check node processing to reduce the complexity and latency for finding the first minimum values. In addition, we introduce a novel second extra column to replace the second minimum values. Then, only the two extra columns are used to generate the check node messages. By using the one-min finder instead of the two-min finder to find the first minimum values, both the complexity and the latency of the CNU are greatly reduced.

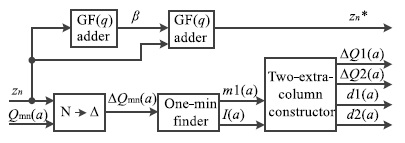

BLOCK DIAGRAM