- ALL COMPUTER, ELECTRONICS AND MECHANICAL COURSES AVAILABLE…. PROJECT GUIDANCE SINCE 2004. FOR FURTHER DETAILS CALL 9443117328

Projects > ELECTRONICS > 2017 > IEEE > VLSI

A linearization technique of voltage-to-frequency characteristics of voltage-controlled oscillator (VCO) analog-to-digital converters (ADCs) is presented. In contrast to previous works, the proposed technique is an open-loop calibration-free configuration, so it can operate at higher frequencies. It is also independent of the delay element structure, so it can be applied to various VCO ADC topologies. The analog input signal is first mapped through a preweighted resistor network in which every delay element experiences a different version of the input and produces the corresponding delay. As a result, the proposed approach suppresses the impact of V/F nonlinearity on the ADC performance by expanding a linear region of the transfer curve over the full rail-to-rail input.

VCO-Based Quantizer, Sigma Delta Modulator.

Calibration-free approach to linearize VCO ADC is presented. The V/F nonlinearity is mitigated by first spreading the analog input over a preweighted resistor network. Binary-weighted and V/F tenability are two attractive features which could open the door for more design improvement. This will enable better SFDR and a wider linear transfer curve. Since the number of stages N (phases) will linearly reduce the VCO gain sensitivity (KVCO) and exponentially increase the resistors values, N should be wisely chosen to get an optimum point.

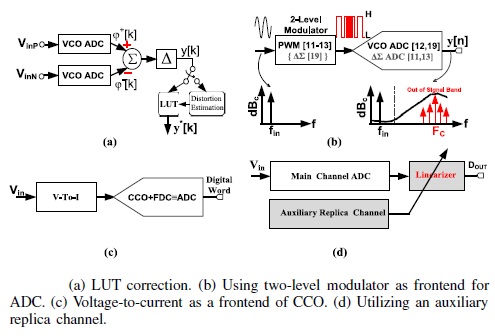

BLOCK DIAGRAM